马上注册,看完整文章,学更多FPGA知识。

您需要 登录 才可以下载或查看,没有帐号?立即注册

x

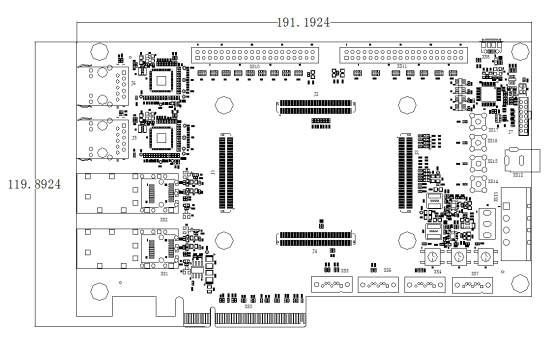

一、开发板简介1.1 产品简介MP5705开发板底板适配本公司相关核心板,型号为MP5650(详见MP5650用户手册)。通过核心板+底板的模式来设计组成完整的开发。底板与核心板采用4个120pin高速板间连接器对插,型号为PANASONIC公司的AXK5A2137YG和AXK6A2337YG。底板按照全高半长PCIE板卡设计,可以直接安装在电脑机箱中使用。 MP5705底板为方便用户进行二次开发,扩展了一系列外围接口。其中包括2路SFP光纤接口、2路千兆以太网接口、4路SATA接口、PCIE x8接口、4路SMA接口、2组40针扩展接口(其中一组全部为差分信号)、板载下载器以及若干按键、LED、板载GTX时钟等。 MP5705底板硬件框图如图1.1所示: 图1.1 MP5705底板硬件框图 1.2 接口列表1.3 产品结构尺寸图产品结构尺寸如图1.3所示: 图1.3 产品结构尺寸图 二、主要接口介绍 2.1 SFP接口板上共2个光模块的发送和接收与J4相连,实现2路高速的光纤通信接口。每一路光模块的电路原理图如图2.1所示: 图2.1 单路光模块电路原理图 每路的光纤数据通信接收和发送的速度高达10.3125Gb/s。用户可以将SFP/SFP+光模块插入到这2个光纤接口中进行光纤数据通信。2路光纤接口与J4连接器相连接。J4连接器与MP5650核心板上FPGA的GTX相连接。SFP/SFP+接口的引脚配置如表2.1所示: 表2.1 SFP/SFP+接口的引脚配置 信号名称 | 连接器管脚 | 对应FPGA管脚名称(MP5650) | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | |

2.2 千兆网接口板上共设计了2路千兆网接口,使用了Realtek公司的RTL8211EG芯片。该芯片是符合10Base-T,100Base-TX和1000Base-T IEEE802.3标准的高集成度的以太网收发器。芯片与MAC之间支持RGMII接口和GMII接口。在MP5705的设计中默认支持RGMII。千兆网接口部分电路原理如图2.2所示: 图2.2 千兆网部分原理图 两路RTL8211EG芯片与核心板之间通过J1相连,千兆网接口的引脚配置表如表2.2所示: 表2.2 千兆网接口引脚配置表 信号名称 | 连接器管脚 | 对应FPGA管脚名称(MP5650) | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | |

2.3 PCIE接口MP5705底板配备了一个PCIE x8 GEN3.0的PCIE接口,为FPGA与处理器通信提供了强大的接口。PCIe具备如下优点: 1) 带宽高,目前FPGA有PCIe Gen3 x16,或者PCIe Gen4 x8,链路速度可以达到128Gbps; 2) FPGA直连,不需要外部PHY; 3) 协议保证数据无误传输,两级CRC,重传机制,保证数据无误; 4) 软件生态丰富,各种系统原生支持,通过简单的驱动就可以完成数据交互; 5) 在PCIe之上的协议逐渐增多,例如NVMe是基于PCIe的上层协议; Xilinx从15年前,V4系列开始,一直在PCIe的解决方案上深耕,提供众多的应用方案级的解决方案,方便用户专注于自己的应用。早期,Xilinx提供的有Application Notes,例如XAPP859,XAPP1052等,构建了基本的双向数据传输。当时一些第三方公司,类似于PLDA,NwLogic也出针对Xilinx FPGA的PCIe传输方案。 后来,Xilinx团队2017年附近推出XDMA解决方案,并持续增加功能、修正Bug,到目前为止,XDMA已经成为一个功能强大、成熟稳定的Xilinx FPGA解决方案。功能上涵盖了SG功能,AXI-Lite功能,多通道分离,AXI-MM和AXI-Stream支持等。稳定性上,经过4年的逐步完善,目前已经有众多的客户基于这套方案实现产品,涵盖医疗、电力、通讯、数据中心等各种应用。 MP5705底板PCIE接口引脚配置表如表2.3所示: 表2.3 PCIE接口引脚配置表 信号名称 | 连接器管脚 | 对应FPGA管脚名称(MP5650) | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | |

2.4 SATA接口MP5705板载4个SATA接口,配合MP5650核心板可实现SATA3.0的全部功能。电路原理图如图2.4所示: 图2.4 SATA接口电路原理图 SATA是一种基于行业标准的串行硬件驱动器接口,以连续串行的方式传输数据,支持热插拔,主要用于SATA主机与大容量存储设备之间的数据传输。目前,SATA一共发展了三代,分别是SATA1、SATA2、SATA3,向后兼容,每一代SATA具有相应的传输功能定义,并且他们的传输速率也不尽相同。SATA1.0的传输速率只有150MB/s,SATA2.0扩展为300MB/s,SATA3.0将端口的传输速率提升至6Gbit/s。 MP5705底板SATA接口引脚配置表如表2.4所示: 表2.4 SATA接口引脚配置表 信号名称 | 连接器管脚 | 对应FPGA管脚名称(MP5650) | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | |

2.5 40针扩展口底板预留了2个2.54mm标准间距的40针的扩展口XS10和XS11,用于连接本公司设计的各个模块或者用户自己设计的模块功能电路,其中XS10上的18组差分信号在PCB布局上全部严格按照差分线布局,用户可以根据自己的需要选择。XS10和XS11的电路原理图如图2.5和2.6所示: 图2.5 XS10电路原理图 图2.6 XS11电路原理图 40针扩展口引脚定义表:略。 2.5 JTAG接口MP5705底板配备了一个板载JTAG电路。用户可以直接用一根MicroUSB线连接到底板即可实现FPGA在线升级和固化。由于该部分电路是直接焊接在底板上,因此不必担心热插拔造成FPGA芯片损坏。此外,MP5705底板还预留了标准2mm间距的14针JTAG接口,用户在购买的时候可以选择是否需要板载JTAG电路。 三、底板电源3.1供电接口底板集成电源管理,支持+6V~+17V宽压输入。电源输入支持两种方式连接。一种为普通的DC-005(2.0)插座,如图3.1所示。一般用于简单的板级调试,可以直接使用12V的电源适配器,具有很强的灵活性。 图3.1 DC-005(2.0)实物照片 另一种方式采用凤凰座进行连接,型号为TE公司的796866-4。实物图如图3.2所示。该连接器耐压高,接触电阻小,抗震性优异,能承受-40℃~+105℃高温。插头与插座之间由锁紧螺丝固定,适合在工业级设备上使用。可直接用于工程样机开发。 图3.2 796866-4实物照片 3.2 电源电路底板共有三种电源,分别是数字5.0V,数字3.3V和模拟3.3V。其中数字5.0V和数字3.3V通过TI公司的电源芯片TPS54620产生。电路如图3.3所示: 图3.3 MP5705数字部分电源原理图 模拟3.3V主要为两路光模块供电,通过ADI公司的LT1963AES8_PBF产生。电路如图3.4所示: 图3.4 MP5705模拟部分电源原理图 想了解核心板更多资料的,可以添加微信:MDYfpga003

|

|手机版|小黑屋|MDYBBS

( 粤ICP备16061416号 )

|手机版|小黑屋|MDYBBS

( 粤ICP备16061416号 )