## IP 核设计(Shift Ram)说明文档

## 1功能描述

输入一幅二值化后的图像,根据腐蚀算法,对图像进行腐蚀,从而去掉零散的边缘点,得到图像的骨干。

关于腐蚀算法的详细解释,请参考 refrence 目录下的《腐蚀膨胀算法详细解释.doc》。

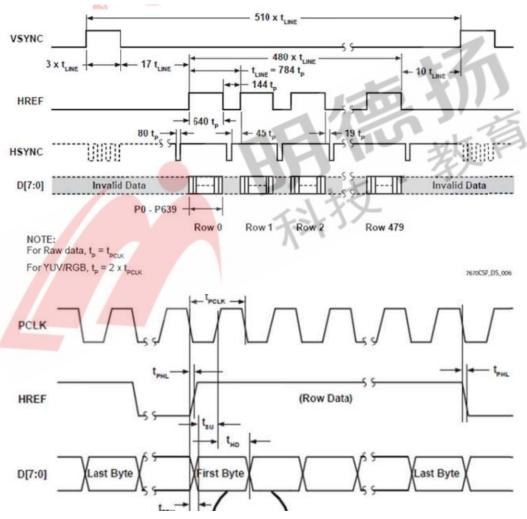

在实现腐蚀算法时,我们需要用到连续几行的图像数据。但在 FPGA 中,图像数据通常是一个一个像素得到的,例如 FPGA 从摄像头采集到的数据顺序,如下图所示:

即 FPGA 先得到第一行的第一个像素,然后是第二个,直到第一行的第 640 个,接下来 是第二行的第一个。

为此,FPGA 必须保存连续几行的数据,然后再从中取每行的几个数据,从而得到运算的矩阵。FPGA 中,运用 shift ram 这个 IP 核即可轻松实现。

本工程实现一个 3X3 矩阵的腐蚀算法。该模块具有如下功能:

1) 模块内部包含一个 shift ram,用于存储 2 行的图像数据,从而得到 3X3 矩阵所需要的像素值。

- 2) 为设计方便,在运算前面两行的图像时,由于得不到 3X3 个数据,所以固定为 0。

- 3) 为设计方便,在运算前面两列的图像时,由于得不到 3X3 个数据,所以固定为 0。

- 4) 输入的图像是二值化后的 640\*480 的图像(即一帧图像有 640\*480 个像素,一行 640 个,共有 480 行),每个像素 1 比特。输入和输出信号定义,请看信号列表。

## 2 信号列表

| 信号名     | I/O | 位宽 | 说明                  |

|---------|-----|----|---------------------|

| clk     | I   | 1  | 50MHz 的写时钟          |

| rst_n   | I   | 1  | 复位信号                |

| dat_in  | I   | 16 | 输入的图像数据             |

| sop_in  | I   | 1  | 输入图像帧的第一个像素点指示信号。   |

| eop_in  | I   | 1  | 输入图像帧的最后一个像素点指示信号   |

| soc_in  | I   | 1  | 输入图像帖,每行的第一个像素指示信号  |

| eoc_in  | I   | 1  | 输入图像帖,每行的最后一个像素指示信号 |

| vld_in  | I   | 1  | 输入图像数据有效指示信号        |

| dat_out | 0   | 8  | 输出的图像数据             |

| sop_out | 0   | 1  | 输出图像帧的第一个像素点指示信号。   |

| eop_out | 0   | 1  | 输出图像帧的最后一个像素点指示信号   |

| soc_out | 0   | 1  | 输出图像帖,每行的第一个像素指示信号  |

| eoc_out | 0   | 1  | 输出图像帖,每行的最后一个像素指示信号 |

| vld_out | 0   | 1  | 输出图像数据有效指示信号        |