# 异步时序之经典CPU接口传输 练习时序参数

点透学习误区 拨出设计精髓

主 讲:潘文明

### 明德扬科教

QQ群: 97925396

官 网: http://www.mdy-edu.com

淘 宝: http://mdy-edu.taobao.com

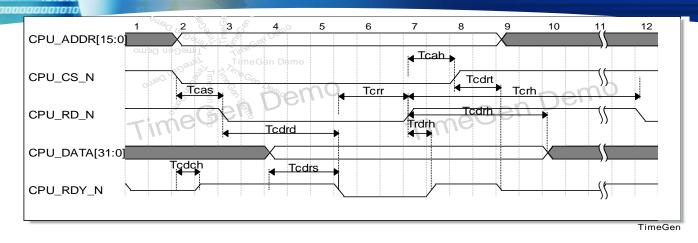

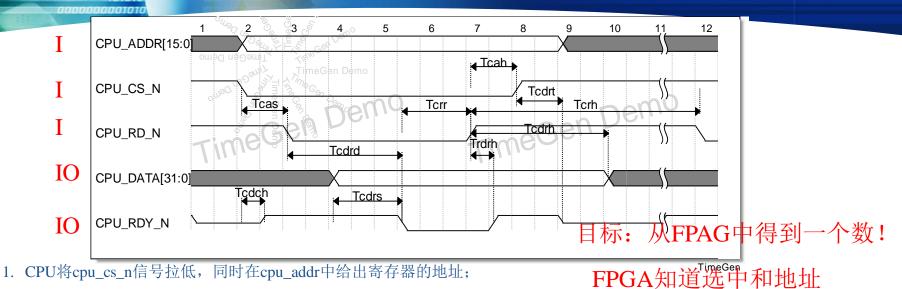

#### 一、读时序

- 1. CPU将cpu\_cs\_n信号拉低,同时在cpu\_addr中给出寄存器的地址;

- 2. FPGA识别出cpu\_cs\_n信号拉低后,将cpu\_rdy\_n信号由输出高阻变成输出高电平;

- 3. CPU将cpu\_rd\_n拉低,告知FPGA这是读操作;

- 4. FPGA识别出读操作后,把寄存器数据输出到cpu\_data上,然后将cpu\_rdy\_n输出低电平,告知CPU数据已经准备好;

- 5. CPU识别出cpu\_rdy\_n的下降沿,将会读取cpu\_data上的值;

- 6. CPU将cpu\_rd\_n拉高;

- 7. FPGA识别出cpu\_rd\_n拉高后,知道cpu已经读走了数据,则将cpu\_rdy\_n信号拉高;

- 8. CPU识别出cpu\_rdy\_n信号拉高后,将cpu\_cs\_n拉高;

- 9. FPGA识别出cpu\_cs\_n拉高后,将cpu\_rdy\_n输出高阻。

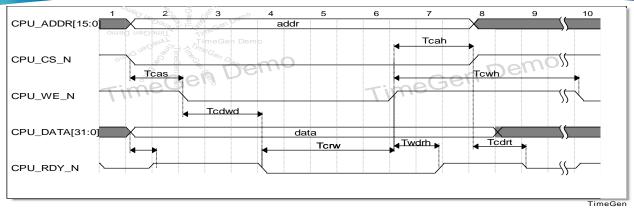

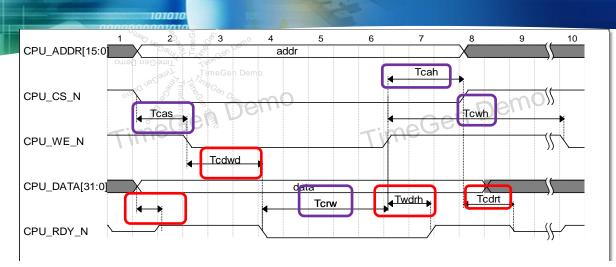

#### 二、写时序

101010 00000000001010

- 1. CPU将cpu\_cs\_n信号拉低,并同时在cpu\_addr中给出寄存器的地址,cpu\_data上给出要写的数据;

- 2. FPGA识别出cpu\_cs\_n信号拉低后,将cpu\_rdy\_n信号由输出高阻变成输出高电平;

- 3. CPU将cpu\_we\_n信号拉低,告知FPGA这是写操作;

- 4. FPGA识别出写操作后,把cpu\_data的值写到cpu\_addr指定的寄存器上,然后cpu\_rdy\_n拉低,告知CPU将写完;

- 5. CPU识别出cpu\_rdy\_n的下降沿,明白FPGA已经写完;

- 6. CPU将cpu\_we\_n拉高;

- 7. FPGA识别出cpu\_we\_n拉高后,将cpu\_rdy\_n信号拉高;

- 8. CPU识别出cpu\_rdy\_n信号拉高后,将cpu\_cs\_n拉高;

- 9. FPGA识别出cpu\_cs\_n拉高后,将cpu\_rdy\_n输出高阻;

- 1. 对于设计模块,哪些是输入;哪些是输出;哪些是双向

- 2. 分清每个步骤的控制方

- 3. 分清每个步骤交流的信息

- 4. 看参数表

- 5. 分清楚哪些参数是对方保证,哪些参数是设计模块要保证

- 6. 设计的原则:对于满足参数的任何输入(无论怎么变),都保证能接收正确;对于输

- 出,在满足时序要求前提下简化设计。

- 1. CPU将cpu\_cs\_n信号拉低,同时在cpu\_addr中给出寄存器的地址;

- 2. FPGA识别出cpu\_cs\_n信号拉低后,将cpu\_rdy\_n信号由输出高阻变成输出高电平;

- 3. CPU将cpu\_rd\_n拉低,告知FPGA这是读操作;

- 4. FPGA识别出读操作后,把寄存器数据输出到cpu\_data上,然后将cpu\_rdy\_n输出低电平,告知CPU数据已经准备好;

- 5. CPU识别出cpu\_rdy\_n的下降沿,将会读取cpu\_data上的值;

- 6. CPU先后将cpu\_rd\_n和cpu\_cs\_n信号拉高;

- 7. FPGA识别出cpu\_rd\_n拉高后,知道cpu已经读走了数据,则将cpu\_rdy\_n信号拉高;

- 8. CPU识别出cpu\_rdy\_n信号拉高后,将cpu\_cs\_n拉高;

- 9. FPGA识别出cpu\_cs\_n拉高后,将cpu\_rdy\_n输出高阻。

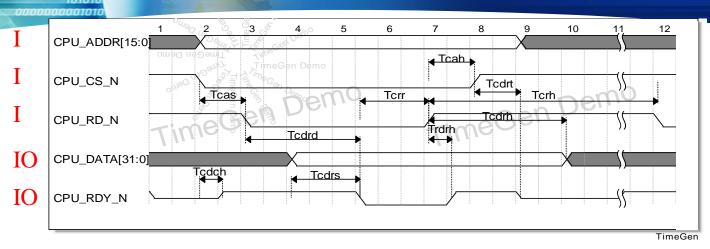

- 1. 对于设计模块,哪些是输入;哪些是输出;哪些是双向

- 2. 分清每个步骤的控制方

- 3. 分清每个步骤交流的信息

- 4. 看参数表

- 5. 分清楚哪些参数是对方保证,哪些参数是设计模块要保证

- 6. 设计的原则:对于满足参数的任何输入(无论怎么变),都保证能接收正确;对于输

- 出,在满足时序要求前提下简化设计。

- 1. CPU将cpu\_cs\_n信号拉低,同时在cpu\_addr中给出寄存器的地址; CPU

- 2. FPGA识别出cpu\_cs\_n信号拉低后,将cpu\_rdy\_n信号由输出高阻变成输出高电平; FPGA

- 3. CPU将cpu\_rd\_n拉低,告知FPGA这是读操作; CPU

#### **FPGA**

- 4. FPGA识别出读操作后,把寄存器数据输出到cpu\_data上,然后将cpu\_rdy\_n输出低电平,告知CPU数据已经准备好;

- 5. CPU识别出cpu\_rdy\_n的下降沿,将会读取cpu\_data上的值; CPU

- 6. CPU先后将cpu\_rd\_n和cpu\_cs\_n信号拉高; CPU

#### **FPGA**

- 7. FPGA识别出cpu\_rd\_n拉高后,知道cpu已经读走了数据,则将cpu\_rdy\_n信号拉高;

- 8. CPU识别出cpu\_rdy\_n信号拉高后,将cpu\_cs\_n拉高;

- **FPGA**

**CPU**

9. FPGA识别出cpu\_cs\_n拉高后,将cpu\_rdy\_n输出高阻。

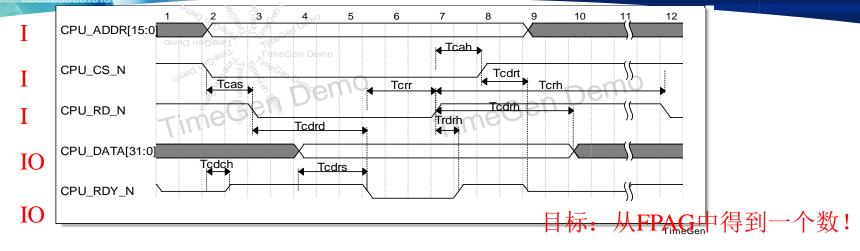

- 1. 对于设计模块,哪些是输入;哪些是输出;哪些是双向

- 2. 分清每个步骤的控制方

- 3. 分清每个步骤交流的信息

- 4. 看参数表

- 5. 分清楚哪些参数是对方保证,哪些参数是设计模块要保证

- 6. 设计的原则:对于满足参数的任何输入(无论怎么变),都保证能接收正确;对于输

- 出,在满足时序要求前提下简化设计。

2. FPGA识别出cpu\_cs\_n信号拉低后,将cpu\_rdy\_n信号由输出高阻变成输出高电平;

CPU选中了FPGA

3. CPU将cpu\_rd\_n拉低,告知FPGA这是读操作;

#### FPGA知道这是读操作C

CPU知道读完成

- 4. FPGA识别出读操作后,把寄存器数据输出到cpu\_data上,然后将cpu\_rdy\_n输出低电平,告知CPU数据已经准备好;

- 5. CPU识别出cpu\_rdy\_n的下降沿,将会读取cpu\_data上的值;

- 6. CPU先后将cpu\_rd\_n和cpu\_cs\_n信号拉高;

#### FPGA知道CPU要结束操作

- 7. FPGA识别出cpu\_rd\_n拉高后,知道cpu已经读走了数据,则将cpu\_rdy\_n信号拉高; CPU知道读结束

- 8. CPU识别出cpu\_rdy\_n信号拉高后,将cpu\_cs\_n拉高;

- 9. FPGA识别出cpu\_cs\_n拉高后,将cpu\_rdy\_n输出高阻。

- 1. 对于设计模块,哪些是输入;哪些是输出;哪些是双向

- 2. 分清每个步骤的控制方

- 3. 分清每个步骤交流的信息

- 4. 看参数表

- 5. 分清楚哪些参数是对方保证,哪些参数是设计模块要保证

- 6. 设计的原则:对于满足参数的任何输入(无论怎么变),都保证能接收正确;对于输

- 出,在满足时序要求前提下简化设计。

| 1. | Tcas: | cs=0到rd=0至少有10ns |

|----|-------|------------------|

|----|-------|------------------|

2. Tcrr: rdy=0到rd=1至少有10ns

3. Tcah: rd=1到cs=1至少有10ns

4. Tcrh: 两次读之间至少有200ns

| Symbal | 描述                                          | Min (ns) | Max(ns) |

|--------|---------------------------------------------|----------|---------|

| Tcas   | Address_chip select setuptime               | 10       | -       |

| Tcah   | Address_chip select holdtime                | 10       | -       |

| Tcrh   | Read high width                             | 200      | -       |

| Tcdrh  | Read data hold time after read de-assertion | 30       | 120     |

| Tcdch  | Chip select assertion to ready high level   | 0        | 60      |

| Tcdrd  | Read data driving delay                     | 80       | 200     |

| Tcrr   | Ready assertion to read de-assertion        | 10       | -       |

| Trdrh  | Read de-assertion to ready de-assertion     | 10       | 80      |

| Tcdrt  | Chip select de-assertion to ready tri-state | 0        | 100     |

| Tcwh   | Write high width                            | 200      | -       |

| Tcdwd  | Write assertion to ready assertion          | 80       | 200     |

| Tcrw   | Ready assertion to write de-assertion       | 10       | -       |

| Tcdrs  |                                             | 10       |         |

| Twdrh  | Write de-assertion to ready de-assertion    | 0        | 80      |

1. Tcdch: cs=0到rdy=1要在0~60ns范围

2. Tcdrd: rd=0到rdy=0在80~200ns范围

3. Tcdrs:数据在总线至rdy=0必须大于

10ns

4. Trdrh: rd=1到rdy=1在10~80ns范围

5. Tcdrt: cs=1到rdy=z在0~100ns范围

6. Tcdrh: rd=1到数据无效在30~120ns

范围

## 二、写时序观察

| 1. | Tcas:  | cs=0到we=0至少有10ns |

|----|--------|------------------|

|    | I cub. |                  |

2. Tcrw: rdy=0到we=1至少有10ns

3. Tcah: we=1到cs=1至少有10ns

4. Tcwh: 两次写之间至少有200ns

| Symbal | 描述                                          | Min (ns) | Max(ns) |

|--------|---------------------------------------------|----------|---------|

| Tcas   | Address_chip select setuptime               | 10       | -       |

| Tcah   | Address_chip select holdtime                | 10       | -       |

| Tcrh   | Read high width                             | 200      | -       |

| Tcdrh  | Read data hold time after read de-assertion | 30       | 120     |

| Tcdch  | Chip select assertion to ready high level   | 0        | 60      |

| Tcdrd  | Read data driving delay                     | 80       | 200     |

| Tcrr   | Ready assertion to read de-assertion        | 10       | -       |

| Trdrh  | Read de-assertion to ready de-assertion     | 10       | 80      |

| Tcdrt  | Chip select de-assertion to ready tri-state | 0        | 100     |

| Tcwh   | Write high width                            | 200      | -       |

| Tcdwd  | Write assertion to ready assertion          | 80       | 200     |

| Tcrw   | Ready assertion to write de-assertion       | 10       | -       |

| Tcdrs  |                                             | 10       |         |

| Twdrh  | Write de-assertion to ready de-assertion    | 0        | 80      |

1. Tcdch: cs=0到rdy=1要在0~60ns范围

2. Tcdwd: we=0到rdy=0在80~200ns

3. Tcdrs:数据在总线至rdy=0必须大于

10ns

4. Twdrh: we=1到rdy=1在10~80ns范围

5. Tcdrt: cs=1到rdy=z在0~100ns范围

- 1. 对于设计模块,哪些是输入;哪些是输出;哪些是双向

- 2. 分清每个步骤的控制方

- 3. 分清每个步骤交流的信息

- 4. 看参数表

- 5. 分清楚哪些参数是对方保证,哪些参数是设计模块要保证

- 6. 设计的原则:对于满足参数的任何输入(无论怎么变),都保证能接收正确;对于输

- 出,在满足时序要求前提下简化设计。

### 明德扬科教

QQ群: 97925396

官 网: http://www.mdy-edu.com

淘 宝: http://mdy-edu.taobao.com

101010 010100<del>000000</del>010